# **CH390** Datasheet

V1.3 https://wch-ic.com

# 1. Overview

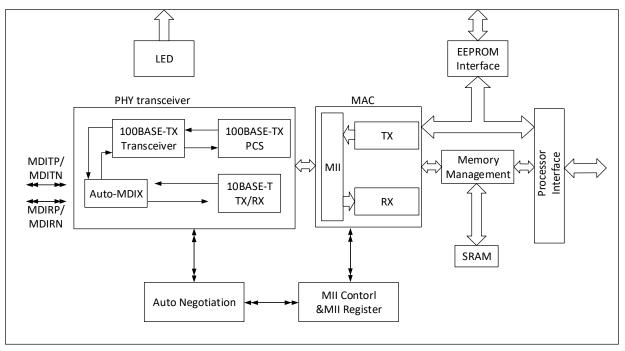

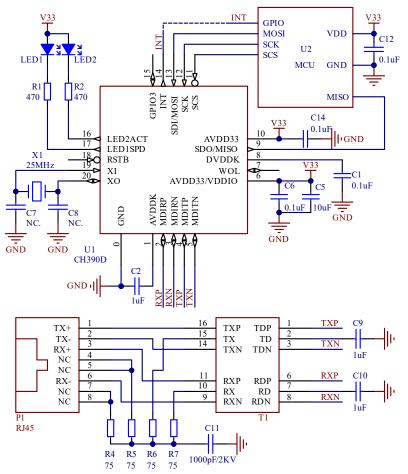

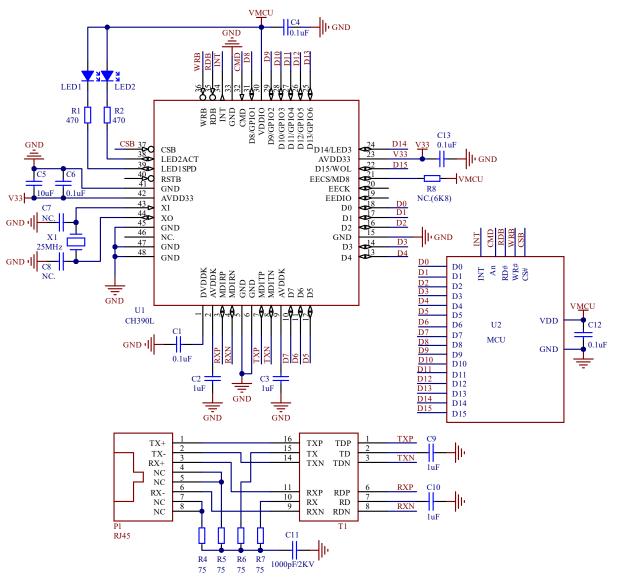

CH390 is an industrial-grade Ethernet controller chip with its own 10/100M Ethernet Media Access Controller (MAC) and Physical Layer (PHY), supporting CAT3, 4, 5 for 10BASE-T and CAT5, 6 for 100BASE-TX connections, supporting HP Auto-MDIX, low-power consumption design, and complying with IEEE 802.3u specification. CH390 has built-in 16K bytes SRAM, supports 3.3V or 2.5V parallel interface and SPI serial interface for compatibility with various MCUs, MPUs, DSPs and other controllers.

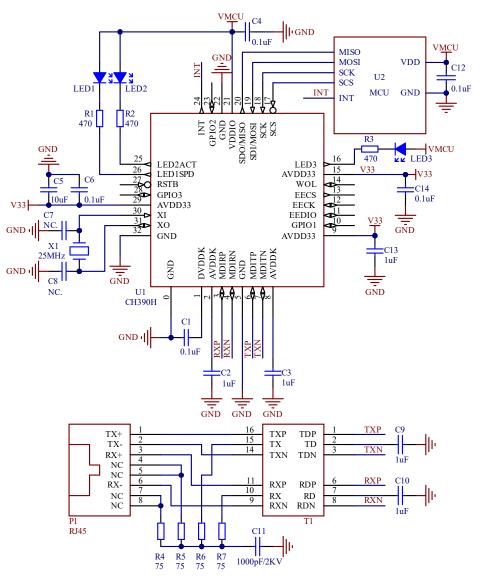

The following figure shows the block diagram of CH390.

# 2. Features

- It comes with its own internal Ethernet Media Access Controller (MAC) and Physical Layer (PHY).

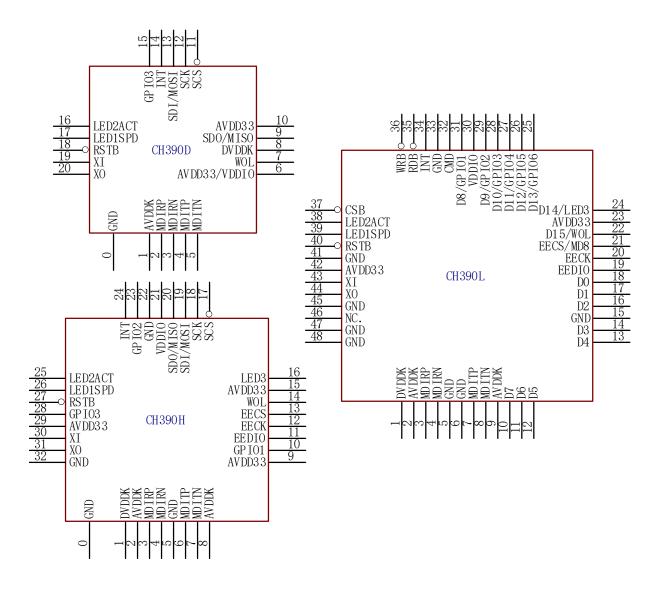

- CH390L supports 8-bit and 16-bit parallel interface, CH390H and CH390D supports SPI serial interface.

- Built-in unique Ethernet MAC address, no additional purchase or distribution, no external EEPROM.

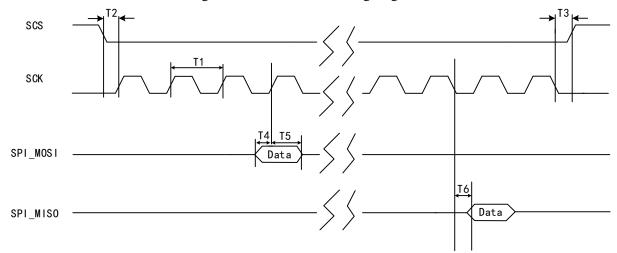

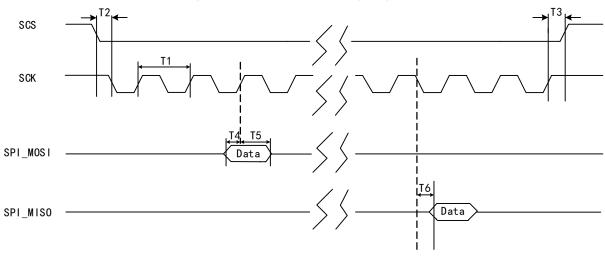

- CH390H/D provides SPI slave interface, supports SPI clock modes 0 and 3 with clock speeds up to 50MHz.

- Integrated low-power 10/100M transceiver based on DSP algorithm implementation Transceiver.

- Support Auto-MDIX to exchange TX/RX and automatically identify positive and negative signal lines.

- Support 10BASE-T and 100BASE-TX and Auto-Negotiation.

- Support UTP CAT5E, CAT6 twisted pair cable, support 120 meters transmission distance.

- Support wake-up frames, link state changes, and magic packet events for remote wake-up.

- Support IEEE 802.3x flow control.

- Support IPv4 TCP/UDP and IPv6 TCP/UDP checksum generation and checking.

- Built-in LDO, CH390H/L support independent I/O interface power supply for different voltage processors or MCUs.

- Built-in  $50\Omega$  matching resistor, built-in crystal oscillator capacitor, with lower BOM cost.

- Support optional external EEPROM configuration chip.

- Small-size QFN20, QFN32 and LQFP48 packages are available.

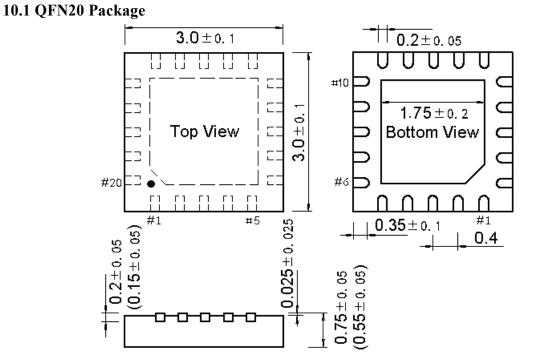

# 3. Package

| Package form | Size      | Pin spacing |         | Package description        | Order model |

|--------------|-----------|-------------|---------|----------------------------|-------------|

| QFN20        | 3.0*3.0mm | 0.40mm      | 15.7mil | Quad Flat No-Lead Package  | CH390D      |

| QFN32×5      | 5.0*5.0mm | 0.50mm      | 19.7mil | Quad Flat No-Lead Package  | СН390Н      |

| LQFP48       | 7.0*7.0mm | 0.50mm      | 19.7mil | Low Profile Quad Flat Pack | CH390L      |

*Note: Pin 0# refers to the EPAD of the QFN package.*

# 4. Pin

| CH390D<br>Pin No. | CH390H<br>Pin No. | CH390L<br>Pin No.       | Pin name         | Туре | Pin description                                                                                                                                                                                                                                                 |

|-------------------|-------------------|-------------------------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2, 3              | 3、4               | 3、4                     | MDIRP \<br>MDIRN | I/O  | Differential input in 10BASE-T/100BASE-TX MDI<br>mode.<br>Differential output in 10BASE-T/100BASE-TX MDIX<br>mode.                                                                                                                                              |

| 4、5               | 6、7               | 7、8                     | MDITP、<br>MDITN  | I/O  | Differential output in 10BASE-T/100BASE-TX MDI<br>mode.<br>Differential input in 10BASE-T/100BASE-TX MDIX<br>mode.                                                                                                                                              |

| 8                 | 1                 | 1                       | DVDDK            | Р    | External 0.1uF (0.1uF $\sim$ 1uF) capacitor to ground should<br>be placed closely to the chip.                                                                                                                                                                  |

| 1                 | 2                 | 2                       | AVDDK            | Р    | External 1uF capacitor to ground should be placed closely to the chip.                                                                                                                                                                                          |

| -                 | 8                 | 9                       | AVDDK            | Р    | Optional pin, external 1uF (0.1uF $\sim$ 1uF) capacitor to ground is recommended.                                                                                                                                                                               |

| 6                 | 29                | 42                      | AVDD33           | Р    | 3.3V main power input, 1uF ground capacitor is<br>recommended to be placed close to the chip.<br>Or $0.1$ uF ~ 4.7uF, supports 10uF but needs to be connected<br>in parallel with 0.1uF.                                                                        |

| 10                | 9、15              | 23                      | AVDD33           | Р    | Optional 3.3V power input.<br>Recommended connection, optional 1uF (0.1uF ~ 4.7uF)<br>capacitor to ground.                                                                                                                                                      |

| -                 | 21                | 30                      | VDDIO            | Р    | <ul> <li>3.3V or 2.5V power input for I/O interface.</li> <li>It is recommended that 0.1uF (0.1uF~1uF) capacitor to ground be placed close to the chip.</li> <li>Note: The VDDIO of the CH390D is shorted to AVDD33 and only supports 3.3V supplies.</li> </ul> |

| 19                | 30                | 43                      | XI               | I    | Crystal input, external 25MHz crystal end is required, or external clock input.                                                                                                                                                                                 |

| 20                | 31                | 44                      | XO               | О    | The crystal output is inverted and needs to be connected externally to the other end of the 25MHz crystal.                                                                                                                                                      |

| 0                 | 0, 5, 32          | 5、6、15、<br>33、41、<br>45 | GND              | Р    | Common ground terminal.                                                                                                                                                                                                                                         |

| -                 | 22                | 47、48                   | GND              | Р    | Optional ground terminal, recommended connection.                                                                                                                                                                                                               |

| 16                | 25                | 38                      | LED2ACT          | 0    | Connection indication LED.<br>In LED mode 1, it is a combination LED of internal PHY<br>link and carrier sense signal.<br>In LED mode 0, it is only the LED of the carrier sense<br>signal of the internal PHY.                                                 |

| 17                | 26                | 39                      | LED1SPD          | О    | Speed indication LED.A low-level output indicates that the internal PHY is operating in 100M mode.                                                                                                                                                              |

| CH390D<br>Pin No. | CH390H<br>Pin No. | CH390L<br>Pin No.      | Pin name        | Туре    | Pin description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------|-------------------|------------------------|-----------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |                   |                        |                 |         | Float indicates that the internal PHY is operating in 10M mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| -                 | 16                | 24                     | LED3            | O, PD   | Full-duplex indication LED.<br>In LED mode 1, a low output indicates that the internal<br>PHY is operating in full-duplex mode, and a float indicates<br>that the internal PHY is operating in half-duplex mode.<br>In LED mode 0, a low-level output indicates that the<br>internal PHY is operating in 10M mode, and a floating<br>level indicates that the internal PHY is operating in 100M<br>mode.<br>More LED modes are controlled by MAC register 57H.<br><i>Note: Not applicable to CH390L's 16-bit mode and<br/>CH390D</i> . |

| -                 | 10、23             | 31、29                  | GPIO1、<br>GPIO2 | I/O, PD | <ul> <li>Bidirectional three-state universal input and output, default is input.</li> <li>Controlled by bit 1 and bit 2 of MAC registers 1Eh, 1Fh.</li> <li><i>Note: The GPIO2 of the CH390D is internally shorted to SDI, disabling the setting of GPIO2.</i></li> </ul>                                                                                                                                                                                                                                                              |

| 15                | 28                | 28                     | GPIO3           | I/O, PD | Bidirectional three-state general-purpose inputs and<br>outputs, defaulting to inputs.<br>Controlled by bit 3 of MAC registers 1Eh, 1Fh.                                                                                                                                                                                                                                                                                                                                                                                               |

| -                 | _                 | 22、24、<br>25~29、<br>31 | D15~D8          | I/O, PD | <ul> <li>Bits 8 ~ 15 of the processor data bus Dbus are used for the 16-bit parallel port.</li> <li>In 16-bit mode, bits 8 to 15 as the processor data bus. In 8-bit mode, as GPIO or application-specific I/O.</li> </ul>                                                                                                                                                                                                                                                                                                             |

|                   |                   | 25~27                  | GPIO6<br>~GPIO4 | O, PD   | In 8-bit mode, it is used as a general-purpose output. These<br>pins can only be used as general-purpose output pins and<br>are controlled by register 1Fh.                                                                                                                                                                                                                                                                                                                                                                            |

| -                 | -                 | 10~14、<br>16~18        | D7~D0           | I/O, PD | Bits 0 to 7 of the processor data bus Dbus are used for 8-<br>bit or 16-bit parallel interfaces.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -                 | 11                | 19                     | EEDIO           | I/O, PD | EEPROM data input and output pins, default is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| -                 | 12                | 20                     | EECK            | O, PD   | EEPROM clock output, default is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| -                 | 13                |                        | EECS            | O, PD   | EEPROM chip select output, active high, default is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                 | -                 | 21                     | MD8             | O, PD   | This pin also serves as the configuration pin for the data<br>width of the CH390L parallel port.<br>During power-on reset, if this pin is in 8-bit mode when<br>pulled high by an external resistor, the data width is 8 bits.<br>Otherwise, it is 16-bit mode with 16-bit data width.                                                                                                                                                                                                                                                 |

| 7                 | 14                | 22                     | WOL             | O, PD   | Network wake-up output, polarity configurable via<br>EEPROM<br>Note: Not applicable to CH390L's 16-bit mode.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11                | 17                | -                      | SCS             | Ι       | SPI chip select input, active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CH390D<br>Pin No. | CH390H<br>Pin No. | CH390L<br>Pin No. | Pin name | Туре  | Pin description                                                                                                                                                                  |

|-------------------|-------------------|-------------------|----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                | 18                | -                 | SCK      | I, PD | SPI clock input, mode 0 or 3 supported.                                                                                                                                          |

| 13                | 19                | -                 | SDI      | I, PD | SPI serial data input, connected to the MOSI of the processor SPI host.                                                                                                          |

| 9                 | 20                | -                 | SDO      | O, PD | SPI serial data output, connected to the MISO of the processor SPI host.                                                                                                         |

| 14                | 24                | 34                | INT      | О     | Interrupt request output, active high by default. The polarity can be set via EEPROM configuration or MAC register 39H.                                                          |

| 18                | 27                | 40                | RSTB     | I, PU | Reset input, active low.                                                                                                                                                         |

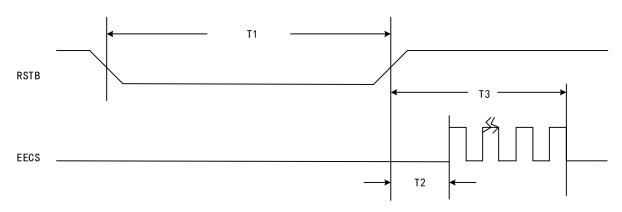

| -                 | -                 | 32                | CMD      | I, PD | Parallel Interface. This cycle command type selection<br>input.<br>Selects access to the data port when high.<br>When low, access to the INDEX address index port is<br>selected |

| -                 | -                 | 35                | RDB      | I, PD | The processor parallel port reads the control signal input.<br>The default is active low and the polarity is configurable<br>via EEPROM.                                         |

| -                 | -                 | 36                | WRB      | I, PD | Processor parallel port write control signal input. The default is active low and the polarity is configurable via EEPROM.                                                       |

| -                 | -                 | 37                | CSB      | I, PU | Processor parallel port chip select input. The default is active low and the polarity is configurable via EEPROM.                                                                |

| -                 | -                 | 46                | NC.      | -     | Empty pins.                                                                                                                                                                      |

*Note: I* = *Input;*

O = Output;

*I/O* = *Input/Output;*

*P* = *Power supply;*

*PD* = *Internal pull-down resistor;*

*PU* = *Internal pull-up resistor.*

# 5. Register Description

Note: In this manual, (H) corresponds to CH390H and CH390D, (L) corresponds to CH390L; if (H) or (L) is not indicated, it applies to CH390H, CH390D and CH390L.

| Register  | Description                                | Offset  | Default value after reset |

|-----------|--------------------------------------------|---------|---------------------------|

| NCR       | Network Control Register                   | 00h     | 00h                       |

| NSR       | Network Status Register                    | 01h     | 00h                       |

| TCR       | TX Control Register                        | 02h     | 00h                       |

| TSRA      | TX Status Register A                       | 03h     | 00h                       |

| TSRB      | TX Status Register B                       | 04h     | 00h                       |

| RCR       | RX Control Register                        | 05h     | 00h                       |

| RSR       | RX Status Register                         | 06h     | 00h                       |

| ROCR      | Receive Overflow Counter Register          | 07h     | 00h                       |

| BPTR      | Back Pressure Threshold Register           | 08h     | 37h                       |

| FCTR      | Flow Control Threshold Register            | 09h     | 38h                       |

| FCR       | RX/TX Flow Control Register                | 0Ah     | 00h                       |

| EPCR      | EEPROM&PHY Control Registers               | 0Bh     | 00h                       |

| EPAR      | EEPROM&PHY Address Registers               | 0Ch     | 40h                       |

| EPDRL     | EEPROM&PHY Low Byte Data Register          | 0Dh     | XXh                       |

| EPDRH     | EEPROM&PHY High Byte Data Register         | 0Eh     | XXh                       |

| WCR       | Wake Up Control Register                   | 0Fh     | 00h                       |

|           |                                            |         | Built-in unique Ethernet  |

| PAR       | Ethernet MAC Physical Address Register     | 10h~15h | address, configurable     |

|           |                                            |         | override by EEPROM        |

| MAR       | Multicast Address Hash Table Register      | 16h~1Dh | XXh                       |

| GPCR      | General-purpose Control Register           | 1Eh     | 71h                       |

| GPR       | General-purpose Register                   | 1Fh     | XXh                       |

| TRPAL     | TX Memory Read Pointer Address Low Byte    | 22h     | 00h                       |

| TRPAH     | TX Memory Read Pointer Address High Byte   | 23h     | 00h                       |

| RWPAL     | RX Memory Write Pointer Address Low Byte   | 24h     | 00h                       |

| RWPAH     | RX Memory Write Pointer Address High Byte  | 25h     | 0Ch                       |

| VID       | Vendor ID                                  | 28h~29h | 1C00h                     |

| PID       | Product ID                                 | 2Ah~2Bh | 9151h(H)/9150h(L)         |

| CHIPR     | CHIP Revision                              | 2Ch     | 2Bh(H)/2Ah(L)             |

| TCR2      | Transmit Control Register 2                | 2Dh     | 00h                       |

| ETXCSR(L) | Early transmission control/status register | 30h     | 00h                       |

| ATCR(H)   | Automatic transmission control register    | 30h     | 00h                       |

| TCSCR     | Transmit Check Sum Control Registers       | 31h     | 00h                       |

| RCSCSR    | Receive Check Sum Control Status Register  | 32h     | 00h                       |

| MPAR      | MII PHY Address Register                   | 33h     | 00h                       |

| LEDCR(L)  | LED Control Register                       | 34h     | 00h                       |

| SBCR(H)   | SPI Bus Control Register                   | 38h     | 44h                       |

| INTCR     | INT Pin Control Register                   | 39h     | 00h                       |

| ALNCR(H)  | SPI Byte Align Error Counter Register      | 4Ah     | 00h                       |

| Table | 5-1 | Register | list |

|-------|-----|----------|------|

| Table | 5-1 | Register | nsı  |

| Register   | Description                                                                          | Offset        | Default value after reset |

|------------|--------------------------------------------------------------------------------------|---------------|---------------------------|

| SCCR       | System Clock Turn ON Control Register                                                | 50h           | 00h                       |

| RSCCR      | Resume System Clock Control Register                                                 | 51h           | XXh                       |

| RLENCR     | RX Packet Length Control Register                                                    | 52h           | 00h                       |

| BCASTCR    | RX Broadcast Control Register                                                        | 53h           | 00h                       |

| INTCKCR(H) | INT Pin Clock Output Control Register                                                | 54h           | 00h                       |

| MPTRCR     | Memory Pointer Control Register                                                      | 55h           | 00h                       |

| MLEDCR(H)  | More LED Control Register                                                            | 57h           | 00h                       |

| MRCMDX     | Memory Data Pre-Fetch Read Command Without<br>Address Increment Register 70h(H)/F0h( |               | XXh                       |

| MRCMDX1    | Memory Read Command Without Pre-Fetch and<br>Without Address Increment Register      | 71h(H)/F1h(L) | XXh                       |

| MRCMD      | MRCMD Memory Data Read Command with Address 72h(H)<br>Increment Register             |               | XXh                       |

| MRRL       | Memory Data Read Address Register Low Byte                                           | 74h(H)/F4h(L) | 00h                       |

| MRRH       | Memory Data Read Address Register High Byte                                          | 75h(H)/F5h(L) | 00h                       |

| MWCMDX     | Memory Data Write Command Without Address<br>Increment Register                      | 76h(H)/F6h(L) | XXh                       |

| MWCMD      | Memory Data Write Command Without Address<br>Increment Register                      | 78h(H)/F8h(L) | XXh                       |

| MWRL       | Memory Data Write Address Register Low Byte                                          | 7Ah(H)/FAh(L) | 00h                       |

| MWRH       | Memory Data Write Address Register High Byte                                         | 7Bh(H)/FBh(L) | 00h                       |

| TXPLL      | TX Packet Length Low Byte Register                                                   | 7Ch(H)/FCh(L) | XXh                       |

| TXPLH      | TX Packet Length High Byte Register                                                  | 7Dh(H)/FDh(L) | XXh                       |

| ISR        | Interrupt Status Register                                                            | 7Eh(H)/FEh(L) | 00h                       |

| IMR        | Interrupt Mask Register                                                              | 7Fh(H)/FFh(L) | 00h                       |

*Note: In the register description, the default form is as follows.*

Reset Value:

- 1 Bit set to logic one

- 0 Bit set to logic zero

- X No default value

- *P* = *Power on reset default value*

*H* = *Hardware reset default value*

*S* = *Software reset default value*

E = Default value from EEPROM

T = Default value from strap pin

h = Hex, format

Reserved bits are undefined on read/write access.

Access Type:

- RO = Read Only

- *RW* = *Read/Write*

- R/C = Read and Clear

- RW/C1 = read/write, clear by write 1

- *WO* = *Write Only*

| Bit | Name     | Description                                                                                                                                                                  | Access | Default<br>value |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|

| 7   | Reserved | Reserved                                                                                                                                                                     | RO     | P0               |

| 6   | WAKEEN   | Enable Wakeup Function.<br>Clearing this bit will also clear all wake-up event states,<br>and this bit will not be affected by a software reset.<br>1 = Enable; 0 = Disable. | RW     | P0               |

| 5   | Reserved | Reserved                                                                                                                                                                     | RO     | 00               |

| 4   | MACPD    | Write after read fetch inverse to enable wake-up frame notification.                                                                                                         | RW     | PS0              |

| 3   | FDX      | Duplex Mode of the Internal PHY.<br>1 = Full-duplex;<br>0 = Half-duplex.                                                                                                     | RO     | PS0              |

| 2:1 | LBK      | Loopback Mode<br>Bit: 2 1<br>0 0 Normal;<br>0 1 MAC internal loopback;<br>1 0 Reserved;<br>1 1 Reserved.                                                                     | RW     | PS00             |

| 0   | RST      | Software Reset and Auto-Clear after 10us<br>1 = Reset state; 0 = Non-reset state.                                                                                            | RW     | PO               |

## 5.1 Network Control Register (00h)

## 5.2 Network Status Register (01h)

| Bit | Name     | Description                                                                                                                                                                                                                                                                                                        | Access | Default<br>value |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------|

| 7   | SPEED    | Speed of Internal PHY<br>This bit has no meaning when LINKST=0.<br>1 = 10Mbps; 0 = 100Mbps.                                                                                                                                                                                                                        | RO     | Х                |

| 6   | LINKST   | Link Status of Internal PHY<br>1 = Link OK; 0 = Link failed.                                                                                                                                                                                                                                                       | RO     | Х                |

| 5   | WAKEST   | Wakeup Event Status<br>Clears by read or write 1. This bit will not be affected<br>after software reset.<br>1 = Wakeup event; 0 = No wakeup event.                                                                                                                                                                 | RW/C1  | P0               |

| 4   | Reserved | Reserved                                                                                                                                                                                                                                                                                                           | RO     | 0                |

| 3   | TX2END   | <ul> <li>TX Packet Index B Complete Status</li> <li>Auto-Clear at begin transmitting of TX packet index B</li> <li>and Auto-Set at the end of transmitting of TX packet</li> <li>index B.</li> <li>1 = Transmit completion or idle of packet index B;</li> <li>0 = Packet index B transmit in progress.</li> </ul> | RW/C1  | PS1              |

| 2 | TX1END | <ul> <li>TX Packet Index A Complete Status</li> <li>Auto-Clear at begin transmitting of TX packet index A</li> <li>and Auto-Set at the end of transmitting of TX packet</li> <li>index A.</li> <li>1 = Transmit completion or idle of packet index A;</li> <li>0 = Packet index A transmit in progress.</li> </ul> | RW/C1 | PS1 |

|---|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| 1 | RXOV   | RX Memory Overflow Status<br>1 = RX memory Overflow; 0 = Non-overflow.                                                                                                                                                                                                                                             | RO    | PS0 |

| 0 | RXRDY  | RX Packet Ready<br>1 = Have packet in RX memory;<br>0 = No packet in RX memory.                                                                                                                                                                                                                                    | RO    | PS0 |

### 5.3 TX Control Register TCR (02h)

| Bit | Name     | Description                                                                                               | Access | Default value |

|-----|----------|-----------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | Reserved | Reserved                                                                                                  | RO     | 0             |

| 6   | TJDIS    | Transmit Jabber Timer (2048 bytes) Control<br>1 = Disabled; 0 = Enable.                                   | RW     | PS0           |

| 5   | Reserved | Reserved                                                                                                  | RO     | 0             |

| 4   | PAD_DIS2 | PAD Appends for Packet Index B<br>1 = Disable; 0 = Enable.                                                | RW     | PS0           |

| 3   | CRC_DIS2 | CRC Appends for Packet Index B<br>1 = Disable; 0 = Enable.                                                | RW     | PS0           |

| 2   | PAD_DIS1 | PAD Appends for Packet Index A<br>1 = Disable; 0 = Enable.                                                | RW     | PS0           |

| 1   | CRC_DIS1 | CRC Appends for Packet Index A<br>1 = Disable; 0 = Enable.                                                | RW     | PS0           |

| 0   | TXREQ    | TX Request. Auto-Clear after Sending Completely<br>1 = Transmit in progress; 0 = No transmit in progress. | RW     | PS0           |

### 5.4 TX Status Register TSRA for Packet Index A(03h)

| Bit | Name | Description                                                       | Access | Default value |

|-----|------|-------------------------------------------------------------------|--------|---------------|

|     |      | Transmit Jabber Time Out                                          |        |               |

| 7   | ТЈТО | It is set to indicate that the transmitted frame is truncated due | RO     | PS0           |

| /   | 1310 | to more than 2048 bytes are transmitted.                          | KU     | F 50          |

|     |      | 1 = Timeout; 0 = Non-timeout.                                     |        |               |

|     |      | Loss of Carrier                                                   |        |               |

| 6   | LC   | It is set to indicate the loss of carrier during the frame        | RO     | PS0           |

| 0   |      | transmission. It is not valid in internal loopback mode.          |        |               |

|     |      | 1 = Loss of carrier; 0 = No carrier have been loss.               |        |               |

|     |      | No Carrier                                                        |        |               |

|     |      | It is set to indicate that there is no carrier signal during the  |        |               |

| 5   | NC   | frame transmission. It is not valid in internal loopback mode.    | RO     | PS0           |

|     |      | 1 = No carrier during transmit;                                   |        |               |

|     |      | 0 = Normal carrier status during transmit.                        |        |               |

| 4   | LCOL     | Late Collision<br>It is set when a collision occurs after the collision window of<br>64 bytes.<br>1 = Late collision; 0 = No late collision.                                  | RO | PS0 |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 3   | COL      | Collision Packet<br>It is set to indicate that the collision occurs during<br>transmission.<br>1 = Have been collision; 0 = No collision.                                     | RO | PS0 |

| 2   | EC       | Excessive Collision<br>It is set to indicate that the transmission is aborted due to 16<br>excessive collisions.<br>1 = 16 excessive collisions; 0 = Less than 16 collisions. | RO | PS0 |

| 1:0 | Reserved | Reserved                                                                                                                                                                      | RO | 0   |

### 5.5 TX Status Register TSRB for Packet Index B(04h)

| Bit | Name     | Description                                                                                                                                                                                                                          | Access | Default value |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | ТЈТО     | Transmit Jabber Time Out<br>It is set to indicate that the transmitted frame is<br>truncated due to more than 2048 bytes are transmitted.<br>1 = Timeout; 0 = Non-timeout.                                                           | RO     | PS0           |

| 6   | LC       | Loss of Carrier<br>It is set to indicate the loss of carrier during the frame<br>transmission. It is not valid in internal loopback mode.<br>1 = Loss of carrier; 0 = No carrier have been loss.                                     | RO     | PS0           |

| 5   | NC       | No Carrier<br>It is set to indicate that there is no carrier signal during<br>the frame transmission. It is not valid in internal<br>loopback mode.<br>1 = No carrier during transmit;<br>0 = Normal carrier status during transmit. | RO     | PS0           |

| 4   | LCOL     | Late Collision<br>It is set when a collision occurs after the collision<br>window of 64 bytes.<br>1 = Late collision; 0 = No late collision.                                                                                         | RO     | PS0           |

| 3   | COL      | Collision Packet<br>It is set to indicate that the collision occurs during<br>transmission.<br>1 = Have been collision; 0 = No collision.                                                                                            | RO     | PS0           |

| 2   | EC       | Excessive Collision<br>It is set to indicate that the transmission is aborted due<br>to 16 excessive collisions.<br>1 = 16 excessive collisions; 0 = Less than 16 collisions.                                                        | RO     | PS0           |

| 1:0 | Reserved | Reserved                                                                                                                                                                                                                             | RO     | 0             |

| Bit | Name     | Description                                                                                                          | Access | Default value |

|-----|----------|----------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | Reserved | Reserved                                                                                                             | RW     | PS0           |

| 6   | WTDIS    | Watchdog Timer Disable<br>1 = When set, the Watchdog Timer (2048 bytes) is disabled;<br>0 = Otherwise it is enabled. | RW     | PS0           |

| 5   | Reserved | Reserved                                                                                                             | RO     | PS0           |

| 4   | DIS_CRC  | Discard CRC Error Packet<br>1 = Enable; 0 = Disable.                                                                 | RW     | PS0           |

| 3   | ALL      | Receive All Multicast<br>To receive packet with multicast destination address<br>1 = Enable; 0 = Disable.            | RW     | PS0           |

| 2   | RUNT     | Receive Runt Packet<br>To receive packet with size less than 64-bytes<br>1 = Enable; 0 = Disable.                    | RW     | PS0           |

| 1   | PRMSC    | Promiscuous Mode<br>To receive packet without destination address checking<br>1 = Enable; 0 = Disable.               | RW     | PS0           |

| 0   | RXEN     | RX Enable<br>1 = Enable; 0 = Disable.                                                                                | RW     | PS0           |

### 5.6 RX Control Register RCR (05h)

# 5.7 RX Status Register RSR (06h)

| Bit | Name | Description                                                                                                                                         | Access | Default value |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | RF   | Runt Frame<br>It is set to indicate that the size of the received frame is<br>smaller than 64 bytes.<br>1 = Affirmative; 0 = Negative.              | RO     | PS0           |

| 6   | MF   | Multicast Frame<br>It is set to indicate that the received frame has a multicast<br>address.<br>1 = Affirmative; 0 = Negative.                      | RO     | PS0           |

| 5   | LCS  | Late Collision Seen<br>It is set to indicate that a late collision is found during<br>the frame reception.<br>1 = Affirmative; 0 = Negative.        | RO     | PS0           |

| 4   | RWTO | Receive Watchdog Time-Out<br>It is set to indicate that it receives more than 2048 bytes.<br>1 = Affirmative; 0 = Negative.                         | RO     | PS0           |

| 3   | PLE  | Physical Layer Error<br>It is set to indicate that a physical layer error is found<br>during the frame reception.<br>1 = Affirmative; 0 = Negative. | RO     | PS0           |

| 2   | AE   | Alignment Error<br>It is set to indicate that the received frame ends with a<br>non-byte aligned. 1 = Affirmative; 0 = Negative.                    | RO     | PS0           |

| 1 | CE  | CRC Error<br>It is set to indicate that the received frame ends with a<br>CRC error.<br>1 = Affirmative; 0 = Negative.                                     | RO | PS0 |

|---|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|

| 0 | FOE | RX Memory Overflow Error<br>It is set to indicate that a RX memory overflow error<br>happens during the frame reception.<br>1 = Affirmative; 0 = Negative. | RO | PS0 |

### 5.8 Receive Overflow Counter Register ROCR (07h)

| Bit | Name | Description                                                                                                                    | Access | Default value |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | RXFU | Receive Overflow Counter Overflow<br>This bit is set when the ROC has an overflow condition.<br>1 = Affirmative; 0 = Negative. | R/C    | PS0           |

| 6:0 | ROC  | Receive Overflow Counter<br>This is a statistic counter to indicate the received<br>packet count upon FIFO overflow.           | R/C    | PS0           |

### 5.9 Back Pressure Threshold Register BPTR (08h)

| Bit | Name     | Description                                    | Access | Default value |

|-----|----------|------------------------------------------------|--------|---------------|

|     |          | Back Pressure High Water Overflow Threshold    |        |               |

|     |          | MAC will generate the jam pattern when RX SRAM |        |               |

| 7:4 | BPHW     | free space is lower than this threshold value. | RW     | PS3           |

|     |          | The default is 3K-byte free space.             |        |               |

|     |          | Note: Do not exceed SRAM size.                 |        |               |

| 3:0 | Reserved | Reserved                                       | RO     | 0             |

### 5.10 Flow Control Threshold Register FCTR (09h)

| Bit | Name | Description                                                                                                                                                                                                                                                                                                         | Access | Default value |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7:4 | HWOT | RX Memory High Water Overflow Threshold<br>Send a pause packet with pause time=FFFFH when the<br>RX memory free space is less than this value. If this<br>value is zero, it means no RX flow control. The default<br>value is 3K-byte free space.<br><i>Note: Do not exceed SRAM size.</i>                          | RW     | PS3           |

| 3:0 | LWOT | RX Memory Low Water Overflow Threshold<br>Send a pause packet with pause time=0000H when RX<br>memory free space is larger than this value. This pause<br>packet is enabled after the high water pause packet is<br>transmitted. The default memory free space is 8K-byte.<br><i>Note: Do not exceed SRAM size.</i> | RW     | PS8           |

### 5.11 RX/TX Flow Control Register FCR (0Ah)

| Bit Name Description Access Default valu |

|------------------------------------------|

|------------------------------------------|

| r |       | i i                                                     |       |      |

|---|-------|---------------------------------------------------------|-------|------|

|   |       | Force TX Pause Packet with 0000H                        |       |      |

| 7 | TXP0  | Set to TX pause packet with pause time field is 0000H.  | RW    | PS0  |

|   |       | Auto-Clears after pause packet transmission completion. |       |      |

|   |       | Force TX Pause Packet with FFFFH                        |       |      |

| 6 | TXPF  | Set to TX pause packet with pause time field is FFFFH.  | RW    | PS0  |

|   |       | Auto-Clears after pause packet transmission completion. |       |      |

|   |       | TX Pause Packet Enable                                  |       |      |

| 5 | TXPEN | Enables the pause packet for high/low water threshold   | RW    | PS0  |

| 5 | IAFEN | control in Full-Duplex mode.                            | K W   | P 50 |

|   |       | 1 = Enable; 0 = Disable.                                |       |      |

|   |       | Back Pressure Mode                                      |       |      |

|   |       | This mode is for Half-Duplex mode only. It generates a  |       |      |

| 4 | BKPA  | jam pattern when any packet comes and RX SRAM is        | RW    | PS0  |

|   |       | over BPHW of MAC register 8H.                           |       |      |

|   |       | 1 = Enable; 0 = Disable                                 |       |      |

|   |       | Back Pressure Mode                                      |       |      |

|   |       | This mode is for Half-Duplex mode only. It generates a  |       |      |

| 3 | BKPM  | jam pattern when a packet's DA matches and RX SRAM      | RW    | PS0  |

|   |       | is over BPHW of MAC register 8H.                        |       |      |

|   |       | 1 = Enable; 0 = Disable.                                |       |      |

|   |       | RX Pause Packet Status, Latch and Read Clearly          |       |      |

|   |       | When there has been packet received, this bit will be   |       |      |

| 2 | RXPS  | latched. This bit is cleared after read.                | R/C   | PS0  |

|   |       | 1 = Has been receive pause packet;                      |       |      |

|   |       | 0 = No pause packet received.                           |       |      |

|   |       | RX Pause Packet Current Status                          |       |      |

| 1 | RXPCS | 1 = Received pause packet timer down-count in progress; | RO    | PS0  |

|   |       | 0 = Pause packet timer value is zero.                   |       |      |

| _ |       | Flow Control Enable                                     | D.117 | DCO  |

| 0 | FLCE  | 1 = Enable; 0 = Disable                                 | RW    | PS0  |

# 5.12 EEPROM & PHY Control Register EPCR(0Bh)

| Bit | Name     | Description                                               | Access | Default value |

|-----|----------|-----------------------------------------------------------|--------|---------------|

| 7:6 | Reserved | Reserved                                                  | RO     | 0             |

|     |          | Reload EEPROM                                             |        |               |

| 5   | REEP     | Set one to reload EEPROM.                                 | RW     | PO            |

|     |          | Driver needs to clear it before to enable this function.  |        |               |

|     | WEP      | Write EEPROM Enable                                       |        |               |

| 4   |          | Set this bit to one before the operation of write EEPROM. | RW     | PO            |

|     |          | 1 = Enable; 0 = Disable.                                  |        |               |

|     |          | EEPROM or PHY Operation Select                            |        |               |

| 3   | EPOS     | 0 = Select EEPROM; $1 = $ Select PHY.                     | RW     | PO            |

|     | LFU5     | Note: The current version only supports PHY, selecting    | ĸw     | FU            |

|     |          | EEPROM is not yet implemented.                            |        |               |

| 2 | ERPRR | EEPROM Read or PHY Register Read Command<br>Set 1 to read EEPROM or PHY register.         | RW | PO |

|---|-------|-------------------------------------------------------------------------------------------|----|----|

| 1 | ERPRW | EEPROM Write or PHY Register Write Command                                                | RW | P0 |

|   |       | Set 1 to write EEPROM or PHY register.<br>EEPROM Access Status or PHY Access Status       |    |    |

| 0 | ERRE  | 1 = The EEPROM or PHY access is in progress<br>0 = Completion of the EEPROM or PHY access | RO | PO |

### 5.13 EEPROM & PHY Address Register EPAR (0Ch)

| Bit | Name     | Description                                                                                   | Access | Default value |

|-----|----------|-----------------------------------------------------------------------------------------------|--------|---------------|

| 7:6 | IPHY ADR | PHY Address bit 1 and 0, the PHY address bit [4:2] is force to 0. Force to 01 in application. | RW     | P01           |

| 5:0 | EROA     | EEPROM Word Address or PHY Register Number.                                                   | RW     | P0            |

# 5.14 EEPROM & PHY Data Register EPDRL/EPDRH (EE\_PHY\_L:0Dh, EE\_PHY\_H:0Eh)

| Bit | Name     | Description                                             | Access | Default value |

|-----|----------|---------------------------------------------------------|--------|---------------|

| 7:0 | EPDRL    | EEPROM or PHY Low Byte Data                             | RW     | PO            |

| /.0 | EE_PHY_L | The low byte data read from or write to EEPROM or PHY.  | KW     | PO            |

| 7.0 | EPDRH    | EEPROM or PHY High Byte Data                            | RW     | PO            |

| 7:0 | EE_PHY_H | The high byte data read from or write to EEPROM or PHY. | ĸw     | P0            |

## 5.15 Wake Up Control Register WCR (0Fh)

| Bit | Name     | Description                                                                                                                                                                            | Access | Default value |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7:6 | Reserved | Reserved                                                                                                                                                                               | RO     | 0             |

| 5   | LINKEN   | Link Status Change Wake up Event<br>To control the link status change event in WOL pin<br>function.<br>This bit will not be affected after software reset.<br>1 = Enable; 0 = Disable. | RW     | P0            |

| 4   | SAMPLEEN | Sample Frame Wake up Event<br>To control the sample frame matched event in WOL pin<br>function.<br>This bit will not be affected after software reset.<br>1 = Enable; 0 = Disable      | RW     | P0            |

| 3   | MAGICEN  | Magic Packet Wake up Event<br>To control the Magic packet event in WOL pin<br>function.<br>This bit will not be affected after software reset.<br>1 = Enable; 0 = Disable              | RW     | P0            |

| 2   | LINKST   | Link Status Change Event Occurred<br>1 = Link change event occurred;<br>0 = No link change event.                                                                                      | RO     | P0            |

| 1   | SAMPLEST | Sample Frame Event Occurred<br>1 = Sample frame matched event occurred;                                                                                                                | RO     | P0            |

|   |         | 0 = No sample frame matched.  |    |    |

|---|---------|-------------------------------|----|----|

|   |         | Magic Packet Event Occurred   |    |    |

| ) | MAGICST | 1 = Magic packet received;    | RO | PO |

|   |         | 0 = No magic packet received. |    |    |

### 5.16 Ethernet MAC Physical Address Register PAR0~PAR5 (PAB0~PAB5:10h~15h)

| Bit | Name | Description                   | Access | Default value |

|-----|------|-------------------------------|--------|---------------|

| 7:0 | PAR5 | Physical Address Byte 5 (15h) | RW     | Е             |

| 7:0 | PAR4 | Physical Address Byte 4 (14h) | RW     | Е             |

| 7:0 | PAR3 | Physical Address Byte 3 (13h) | RW     | Е             |

| 7:0 | PAR2 | Physical Address Byte 2 (12h) | RW     | Е             |

| 7:0 | PAR1 | Physical Address Byte 1 (11h) | RW     | Е             |

| 7:0 | PAR0 | Physical Address Byte 0 (10h) | RW     | Е             |

Note: Each chip has a unique Ethernet MAC address built in and will replace this built-in address if the EEPROM configuration data is valid.

### 5.17 Ethernet MAC Physical Address Register MAR0~MAR7(MAB0~MAB5:16h~1Dh)

| Bit | Name | Description                               | Access | Default value |

|-----|------|-------------------------------------------|--------|---------------|

| 7:0 | MAR7 | Multicast Address Hash Table Byte 7 (1Dh) | RW     | Х             |

| 7:0 | MAR6 | Multicast Address Hash Table Byte 6 (1Ch) | RW     | Х             |

| 7:0 | MAR5 | Multicast Address Hash Table Byte 5 (1Bh) | RW     | Х             |

| 7:0 | MAR4 | Multicast Address Hash Table Byte 4 (1Ah) | RW     | Х             |

| 7:0 | MAR3 | Multicast Address Hash Table Byte 3 (19h) | RW     | Х             |

| 7:0 | MAR2 | Multicast Address Hash Table Byte 2 (18h) | RW     | X             |

| 7:0 | MAR1 | Multicast Address Hash Table Byte 1 (17h) | RW     | Х             |

| 7:0 | MAR0 | Multicast Address Hash Table Byte 0 (16h) | RW     | Х             |

### 5.18 General-purpose Control Register (1Eh)

| Bit | Name     | Description                                                  | Access | Default value |

|-----|----------|--------------------------------------------------------------|--------|---------------|

| 7   | Reserved | Reserved                                                     | RO     | PH0           |

|     |          | Define the input/output direction of pin GPIO6~4.            |        |               |

| 6:4 | GPC64    | These bits are forced to "1" and pins GPIO6 to 4 can only be | RO     | P111          |

|     |          | output.                                                      |        |               |

|     |          | Define the input/output direction of pin GPIO3.              |        |               |

| 3   | GPC3     | 1 = Pin GPIO3 in output mode;                                | RW     | PO            |

|     |          | 0 = Pin GPIO3 in input mode.                                 |        |               |

|     |          | Define the input/output direction of pin GPIO2.              |        |               |

| 2   | GPC2     | 1 = Pin GPIO2 in output mode; $0 = Pin GPIO3$ in input mode. | RW     | PO            |

| 2   | 0102     | Note: The CH390D's GPIO2 is internally shorted to SDI,       | IX W   | 10            |

|     |          | disabling the setting of this bit to 1.                      |        |               |

|     |          | Define the input/output direction of pin GPIO1.              |        |               |

| 1   | GPC1     | 1 = Pin GPIO1 in output mode;                                | RW     | PO            |

|     |          | 0 = Pin GPIO1 in input mode.                                 |        |               |

| 0   | Reserved | Reserved                                                     | RO     | P1            |

Note: CH390L This register is applicable to 8-bit mode, for 16-bit mode, refer to register 34h.

### 5.19 General-purpose Register (1Fh)

| Bit | Name     | Description                                                                                                                                                                                                                                                                                   | Access | Default value |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | Reserved | Reserved                                                                                                                                                                                                                                                                                      | RO     | 0             |

| 6:4 | GPO      | The output data of GPIO6 ~ 4 is only applicable to the 8-bit<br>mode of CH390L.<br>These bits are output to pins GPIO6~4, respectively.<br><i>Note: These bits of CH390H and CH390D are reserved</i> .                                                                                        | RW     | PO            |

| 3   | GPIO3    | Output data or input status of GPIO3.<br>When GPC3 of register 1EH is 1, the value of this bit is<br>reflected to pin GP3.<br>When GPC3 of register 1EH is 0, the value of this bit to be<br>read is reflected from correspondent pin of GP3.                                                 | RW     | PO            |

| 2   | GPIO2    | Output data or input status of GPIO2.<br>When GPC2 of register 1EH is 1, the value of this bit is<br>reflected to pin GPIO2.<br>When GPC2 of register 1EH is 0, the value of this bit to be<br>read is reflected from correspondent pin of GPIO2.                                             | RW     | PO            |

| 1   | GPIO1    | Output data or input status of GPIO1.<br>When GPC1 of register 1EH is 1, the value of this bit is<br>reflected to pin GPIO1.<br>When GPC1 of register 1EH is 0, the value of this bit to be<br>read is reflected from correspondent pin of GPIO1.                                             | RW     | РО            |

| 0   | PHYPD    | <ul> <li>PHY Power Down Control, Sleep mode setting.</li> <li>1 = Power down PHY;</li> <li>0 = Power up PHY.</li> <li>In Sleep mode, power off the PHY but keep the system clock module on.</li> <li>Note: If restarting PHY power, it is recommended to access CH390 after 100us.</li> </ul> | RW     | PE1           |

Note: CH390L The GPO and GPIO in this register are only applicable to 8-bit mode, for 16-bit mode, refer to register 34h.

### 5.20 TX Memory Read Pointer Address Register TRPAL/TRPAH(22h~23h)

| Bit | Name  | Description                                    | Access | Default value |

|-----|-------|------------------------------------------------|--------|---------------|

| 7:0 | TRPAH | TX Memory Read Pointer Address High Byte (23h) | RO     | PS0           |

| 7:0 | TRPAL | TX Memory Read Pointer Address Low Byte (22h)  | RO     | PS0           |

### 5.21 RX Memory Write Pointer Address Register RWPAL/RWPAH(24h~25h)

| Bit | Name  | Description                                     | Access | Default value |

|-----|-------|-------------------------------------------------|--------|---------------|

| 7:0 | RWPAH | RX Memory Write Pointer Address High Byte (25h) | RO     | PS,0Ch        |

| 7:0 | RWPAL | RX Memory Write Pointer Address Low Byte (24h)  | RO     | PS,00h        |

### 5.22 Vendor ID Register VIDL/VIDH (28h~29h)

| Bit Name Description Access | Default value |

|-----------------------------|---------------|

|-----------------------------|---------------|

| ľ | 7:0 | VIDH | Vendor ID High Byte (29h) | RO | PE,1Ch |

|---|-----|------|---------------------------|----|--------|

|   | 7:0 | VIDL | Vendor ID Low Byte (28h)  | RO | PE,00h |

### 5.23 Product ID Register PIDL/PIDH (2Ah~2Bh)

| Bit | Name | Description                | Access | Default value    |

|-----|------|----------------------------|--------|------------------|

| 7:0 | PIDH | Product ID High Byte (2Bh) | RO     | PE,91h           |

| 7:0 | PIDL | Product ID Low Byte (2Ah)  | RO     | PE,51h(H)/50h(L) |

### 5.24 Chip revision identification code CHIPR (2Ch)

| Bit | Name  | Description   | Access | Default value   |

|-----|-------|---------------|--------|-----------------|

| 7:0 | CHIPR | CHIP Revision | RO     | P,2Bh(H)/2Ah(L) |

### 5.25 Transmit control register 2 TCR2 (2Dh)

| Bit | Name     | Description                                                                                                                                                                                  | Access | Default value |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | LED      | LED Mode<br>1 = LED mode 1;<br>0 = LED mode 0.                                                                                                                                               | RW     | PE0           |

| ,   |          | The default is mode 0, which can be configured via EEPROM.<br>For CH390H/D, more configurations can be found in register 57h.                                                                |        | 120           |

| 6   | RLCP     | Retry Late Collision Packet<br>Re-transmit the packet with late-collision.<br>1 = Enable; 0 = Disable.                                                                                       | RW     | P0            |

| 5:4 | Reserved | Reserved                                                                                                                                                                                     | RW     | P0            |

| 3:0 | IFGS     | Inter-Frame Gap Setting<br>0XXX = 96-bit;<br>1000 = 64-bit;<br>1001 = 72-bit;<br>1010 = 80-bit;<br>1011 = 88-bit;<br>1100 = 96-bit;<br>1101 = 104-bit;<br>1110 = 112-bit;<br>1111 = 120-bit. | RW     | Р00           |

## 5.26 Early Transmit Control/Status Register (L) ETXCSR (30h)

| Bit | Name     | Description                                                | Access | Default value |

|-----|----------|------------------------------------------------------------|--------|---------------|

| 7   | I ETE    | Early Transmit Enable<br>1: Enable bits [2:0]; 0: DISABLE. | RW     | PS0           |

| 6   | Reserved | Reserved                                                   | RO     | PS0           |

| 5   | Reserved | Reserved                                                   | RO     | PS0           |

| 4:2 | Reserved | Reserved                                                   | RO     | 000           |

|     |          | Early Transmit Threshold                                   |        |               |

|     |          | Start transmit when data write to TX FIFO reach the byte-  |        |               |

|     |          | count threshold.                                           |        |               |

|     |     | Bit-1 | Bit-0 | Threshold |

|-----|-----|-------|-------|-----------|

|     |     | 0     | 0     | 12.5%     |

| 1:0 | ETT | 0     | 1     | 25%       |

|     |     | 1     | 0     | 50%       |

|     |     | 1     | 1     | 75%       |

### 5.27 Auto-Transmit Control Register (H) ATCR (30h)

| Bit | Name     | Description                                                                                                                                                                                                          | Access | Default value |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7   | _        | Auto-Transmit Control<br>1 = Auto-Transmit enabled. Packet transmitted automatically<br>when end of write TX buffer<br>0 = Auto-Transmit disabled. When transmit packet, need to set<br>MAC register 2H bit 0 to "1" | RW     | PS0           |

| 6:2 | Reserved | Reserved                                                                                                                                                                                                             | RO     | P00           |

| 1:0 | Reserved | Reserved                                                                                                                                                                                                             | RW     | PS0           |

### 5.28 Transmit Check Sum Control Register TCSCR (31h)

| Bit | Name       | Description                                              | Access | Default value |

|-----|------------|----------------------------------------------------------|--------|---------------|

| 7:5 | Reserved   | Reserved                                                 | RO     | 0             |

| 4   | IPv6TCPCSE | IPv6 TCP CheckSum Generation<br>1 = Enable; 0 = Disable. | RW     | PS0           |

| 3   | IPv6UDPCSE | IPv6 UDP CheckSum Generation<br>1 = Enable; 0 = Disable. | RW     | PS0           |

| 2   | UDPCSE     | UDP CheckSum Generation<br>1 = Enable; 0 = Disable.      | RW     | PS0           |

| 1   | TCPCSE     | TCP CheckSum Generation<br>1 = Enable; 0 = Disable.      | RW     | PS0           |

| 0   | IPCSE      | IP CheckSum Generation<br>1 = Enable; 0 = Disable.       | RW     | PS0           |

### 5.29 Receive Check Sum Status Register RCSCSR (32h)

| Bit | Name   | Description                                     | Access | Default value |

|-----|--------|-------------------------------------------------|--------|---------------|

| 7   | UDPS   | UDP CheckSum Status                             | RO     | PS0           |

| /   | UDP5   | 1 = Checksum fail; $0 =$ No UDP checksum error. | KU     | P 50          |

| 6   | TCPS   | TCP CheckSum Status                             | RO     | PS0           |

| 0   | ICFS   | 1 = Checksum fail; $0 =$ No TCP checksum error. | KU     | P 50          |

| 5   | 5 IPS  | IP CheckSum Status                              | RO     | PS0           |

| 5   | 11.2   | 1 = Checksum fail; $0 =$ No IP checksum error.  |        |               |

| 4   | UDPP   | UDP Packet of Current Received Packet           | RO     | PS0           |

| 4   | 4 UDPP | 1 = UDP packet; $0 = Non UDP$ packet.           | KU     |               |

| 3   | 3 TCPP | TCP Packet of Current Received Packet           | RO     | PS0           |

| 5   |        | 1 = TCP packet; 0 = Non TCP packet.             | KU     | 130           |

| 2   | IPP    | IP Packet of Current Received Packet            | RO     | PS0           |

|   |       | 1 = IP packet; $0 = Non IP$ packet.                                                        |    |      |

|---|-------|--------------------------------------------------------------------------------------------|----|------|

|   |       | Receive CheckSum Checking Enable<br>When set, the checksum status (bit 7~2) will be stored |    |      |

| 1 | RCSEN | in bit 7:2 of packet's first byte of RX packets status                                     | RW | PS0  |

|   |       | header respectively.                                                                       |    |      |

|   |       | 1 = Enable; 0 = Disable.                                                                   |    |      |

|   |       | Discard CheckSum Error Packet                                                              |    |      |

| 0 | DCSE  | When set, if IPv4/TCP/UDP checksum field is error,                                         | DW | PS0  |

|   | DUSE  | this packet will be discarded.                                                             | RW | P 50 |

|   |       | 1 = Enable; 0 = Disable.                                                                   |    |      |

## 5.30 MII PHY Address Register MPAR (33h)

| Bit | Name     | Description                                    | Access | Default value |

|-----|----------|------------------------------------------------|--------|---------------|

| 7   | ADR_EN   | Redefine PHY Address<br>1: Enable; 0: Disable. | RW     | HPS0          |

| 6:5 | Reserved | Reserved                                       | RO     | HPS0          |

| 4:0 | EPHYADR  | Redefined PHY Address Bit 4~0.                 | RW     | HPS01         |

## 5.31 LED Pin Control Register (L) LEDCR (34h)

| Bit | Name     | Description                                                                                                                                                                                                                                                                                   | Access | Default value |

|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7:2 | Reserved | Reserved                                                                                                                                                                                                                                                                                      | RO     | PS0           |

| 1   | GPIO     | LED act as General-purpose signals in 16-bit mode<br>1: Pin 38/39 (LED2/1) act as the general-purpose pins that are<br>controlled by registers 1Eh bit 2/1 and 1Fh bit 2/1 respectively.<br>0: Disable.                                                                                       | RW     | P0            |

| 0   | MII      | LED act as SMI signals in 16-bit mode<br>1: Pin 38/39 (LED2/1) act as the MII Management Interface<br>mode. In this mode, the LED1 act as data (MDIO) signal and<br>the LED2 act as sourced clock (MDC) signal. These two-pin<br>are controlled by registers 0Bh,0Ch, and 0Dh.<br>0: Disable. | RW     | P0            |

### 5.32 SPI Bus Control Register (H) SBCR (38h)

| Bit | Name      | Description                                                      | Access | Default value |

|-----|-----------|------------------------------------------------------------------|--------|---------------|

| 7:5 | Reserved  | Reserved                                                         | RO     | PO            |

| 4:3 | Reserved  | Reserved                                                         | RO     | P00           |

| 2   | SCS_SPIKE | Eliminate SPI_CSB Spike<br>1 = Eliminate about 2ns SPI_CSB spike | RW     | PE1           |

| 1:0 | Reserved  | Reserved                                                         | RO     | P00           |

## 5.33 INT Pin Control Register INTCR (39h)

| Bit | Name     | Description                 | Access | Default value |

|-----|----------|-----------------------------|--------|---------------|

| 7:2 | Reserved | Reserved                    | RO     | PS0           |

| 1   | INT_TYPE | INT Pin Output Type Control | RW     | PET0          |

|   |   |         | 1 = INT Open-drain output; $0 = INT$ push-pull output.               |    |      |

|---|---|---------|----------------------------------------------------------------------|----|------|

| ( | ) | INT_POL | INT Pin Polarity Control<br>1 = INT active low; 0 = INT active high. | RW | PET0 |

### 5.34 SPI Byte Align Error Counter Register (H) ALNCR (4Ah)

| Bit | Name    | Description                                                                                                                                                       | Access | Default value |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|

| 7:0 | AIN FRR | SPI Clock Byte Align Error Counter<br>The counter to count the byte align error of SCK at end of<br>CSN. The maximum value is 255. Write any value to clear<br>0. | RO     | P00           |

### 5.35 System Clock Turn ON Control Register SCCR(50h)

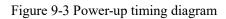

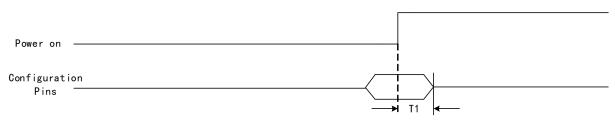

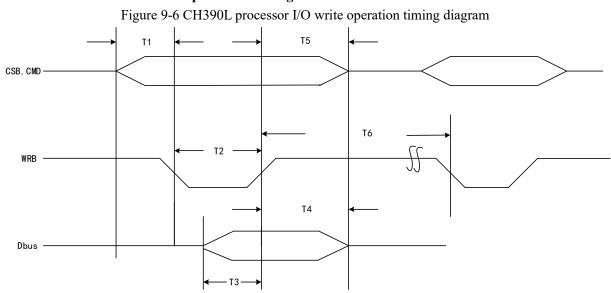

| Bit | Name                                                                                                    | Description |   | Default value |